|

i am learning vhdl and i get an error when i simulate a 3-bit full adder that implements with std_logic_vector (because of ability to use '+' operation)just an example that our teacher gave us,forgive me if it is a simple question...here is code :

i get an error when temp is trying to add 0's at then end of 2 bit arrays,which it says :

every body here is the working code:

Hosein Afshar

Hosein AfsharHosein Afshar

1 Answer

Without any additional libraries, you cannot add signals of type

std_logic_vector. There is no + operator defined that takes two std_logic_vector arguments. The correct way to do this is to include the numeric_std package and cast your arguments to unsigned for your additions.

In practice, most people don't create a whole entity for such a simple operation so there are fewer casts as your signals are in the correct type for the data already (numbers use unsigned, collections of bits use std_logic_vector), which is why this looks a bit awkward.

You could also get by doing this with the synopsis package (std_logic_unsigned) and it would look a little cleaner (no casts), but that package is not part of the VHDL standard and its use has been deprecated.

QuantumRippleQuantumRipple

Got a question that you can’t ask on public Stack Overflow? Learn more about sharing private information with Stack Overflow for Teams.

Not the answer you're looking for? Browse other questions tagged vhdloperation or ask your own question.Adder Subtractor Vhdl

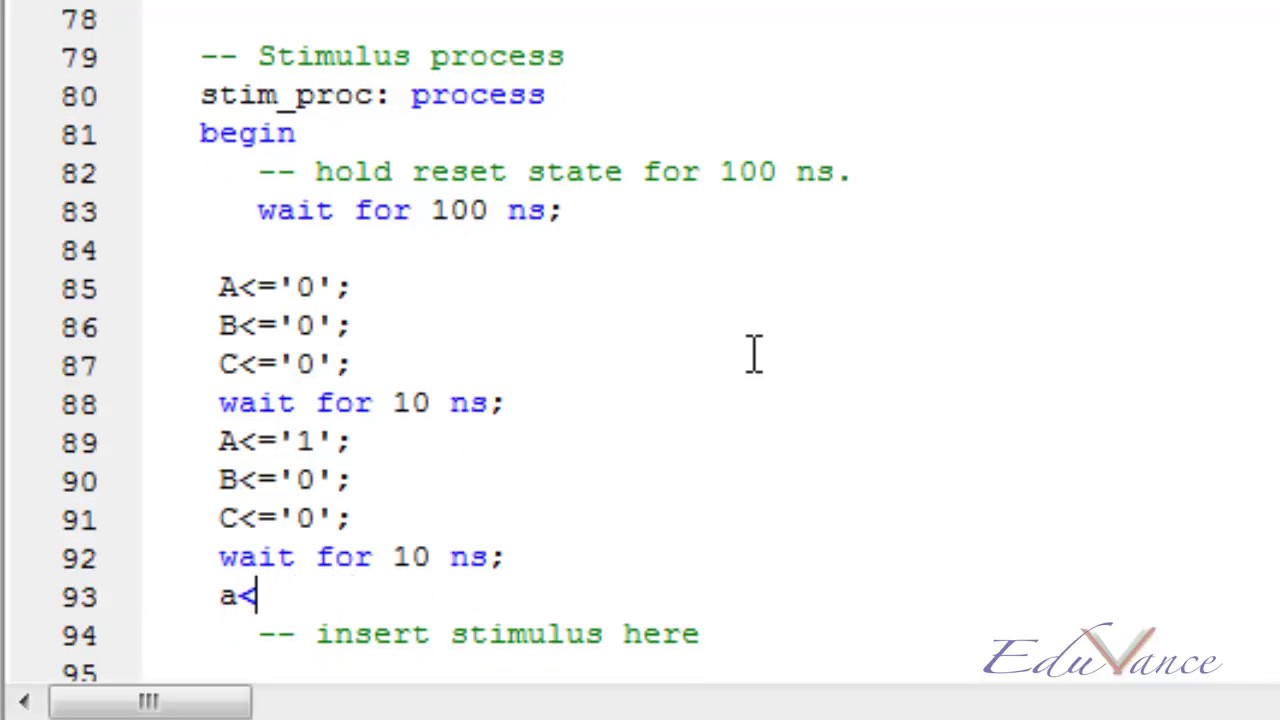

i am a bit new to VHDL and i try to learn by examples. So long story short i began with some basic examples like creating this Full Adder.

After that i tried to implement this 4-bit adder

And this is the code that i wrote.

Also i used a 4_bit_adder test bench file and i found out that the output is right. Now i am trying to implement a 4 bit multiplier with the usage of the 4 bit adder but i am a bit stuck. Actually this is the multiplier that i am trying to implement.

the code i wrote is this, but i am stuck at the port map

Ioan KatsIoan Kats

1 Answer

'I am stuck on the port map' isn't a specific problem statement.

With named association members of formal ports in maps could be associated individually as well as in whole as long as all members of the formal are associated - IEEE Std 1076-2008 6.5.7 Association lists:

A formal interface object shall be either an explicitly declared interface object or member (see 5.1) of such an interface object. In the former case, such a formal is said to be associated in whole. In the latter cases, named association shall be used to associate the formal and actual; the subelements of such a formal are said to be associated individually. Furthermore, every scalar subelement of the explicitly declared interface object shall be associated exactly once with an actual (or subelement thereof) in the same association list, and all such associations shall appear in a contiguous sequence within that association list. Each association element that associates a slice or subelement (or slice thereof) of an interface object shall identify the formal with a locally static name.

Note you have too many carry elements (only need two), don't need andgate(0), don't need sumout(0), sumout(4) or sumout(11 downo 8), there's an extraneous character in the multy architecture, you're missing context clauses and have unused use clauses.

Your code using array intermediary signals:

And a borrowed testbench to demonstrate:

Full Adder Behavior

The to_string function is included for pre -2008 simulators. Context clauses were added to FA and Ripple_Adder.

Full Adder Test Benchuser1155120user1155120

12.5k33 gold badges2323 silver badges2828 bronze badges

Got a question that you can’t ask on public Stack Overflow? Learn more about sharing private information with Stack Overflow for Teams.

Not the answer you're looking for? Browse other questions tagged vhdlfpgamultiplication or ask your own question.Comments are closed.

|

Details

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

- New Page

- Home

- New Page

- About Brooke

- Blog

- Winrar 64 Bit Download Kostenlos

- Contact

- Mass Effect 2 Zaeed Loyalty

- The Crew Wild Run Free Download

- Delete Avast Safe Price

- Beetle Mania Free Slot Game

- Into The Badlands Season 4

- Visual Studio 2010 Express

- Pentair 461059 Master Temp 125k Btu Natural Gas Swimming Pool Heater

- Exedy Civic Si Clutch

- Mens Elbow Patch Sweater

- Fallout 3 Goty English Language Pack Download

- Portal 2 Time Travel

- Spirit Soup: The Queensbury Curse Free Download

- Mirando Al Sol Libro Epub

- Eroge! H Mo Game Mo Kaihatsu Zanmai

- What Is A Cpu Meter On A Computer

- The Adventure Pals Download

- Midiafire Com Download Minecraft

RSS Feed

RSS Feed